|

| 인텔이 IEDM2023에서 공개한 ‘후면 직접 접촉 기술’.(이미지=인텔) |

미국 반도체 기업 인텔이 신기술로 한계에 다다른 것으로 여겨지던 무어의 법칙을 지속한다.

미국 인텔은 9일(현지시간)부터 오는 13일까지 미국 캘리포니아에서 열리는 2023 국제전자소자학회(IEDM)에서 미래 반도체 공정 로드맵을 지원할 연구개발(R&D) 성과를 발표한다. 대상은 △반도체 후면 직접 접촉 기술 △3D 적층 등 혁신기술이다.

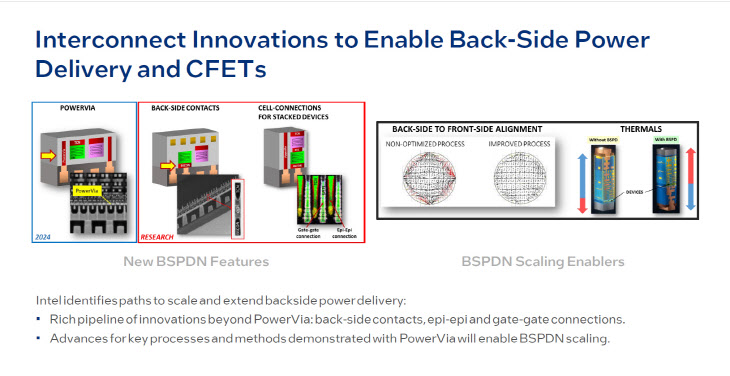

업계의 관심은 인텔의 핵심 기술로 여기겨진 후면 직접 접촉 기술(BSPDN)이다. 기존 반도체는 웨이퍼 전면에 전력 배선이 위치해 있었으나, 이 기술은 웨이퍼 후면에서 전력을 공급한다. 이를 통해 전력과 신호의 상호 연결 병목 현상을 해결할 수 있다는 발상의 전환이다.

앞서 6월 인텔은 후면 전력 공급 기술 파워비아(PowerVia)가 적용된 시제품 ‘블루스카이 크릭’을 공개한 바 있다. 파워비아와 후면 직접 접촉 기술은 인텔이 독자 개발한 기술로 ‘무어의 법칙’을 이어나갈 비밀병기로 불린다.

무어의 법칙은 약 2년마다 최소한의 비용 증가로 반도체 집적회로에 집적할 수 있는 트랜지스터 숫자가 두 배씩 증가한다는 법칙이다. 최근 반도체 미세 공정이 한계에 다다르며 업계에서는 무어의 법칙이 깨졌다는 의견이 주를 이뤘다.

인텔은 이 기술을 통해 업계 최초로 ‘3D 적층’ 기술 CFET(상보형전계효과 트랜지스터)를 선보인다. 기존 시스템 반도체는 트랜지스터를 옆에 붙이는 형태였으나, 메모리 반도체와 같이 수직으로 칩을 쌓으며 반도체에 더 많은 트랜지스터를 넣을 수 있게 됐다.

마우로 코브린스키(Mauro Kobrinsky) 인텔 펠로우는 “비아(신호를 연결하는 구멍)를 위한 공간 확보 필요성이 없어졌기 때문에 더 낮은 전력으로 더 빠르게 칩을 구동할 수 있다”며 “면적이 절약되므로 단위 면적당 더 많은 장치를 장착할 수 있게 됐다”고 설명했다.

인텔 후면 직접 접촉 기술은 내년 양산 예정인 인텔 20A, 18A 공정부터 적용된다. 20A는 2nm(나노미터, 10억분의 1m)급, 18A는 1.8나노급 칩이다. 대만 TSMC는 해당 기술을 2026년부터 적용한다고 밝힌 바 있다. 인텔이 TSMC보다 2년 빠른 셈이다.

다만 CFET 기술은 아직 로드맵에 반영되지 않았다. 18A가 상용화되는 2025년 이후 적용될 예정이다.

이외에도 인텔은 실리콘(Si) 트랜지스터와 질화갈륨(GaN) 트랜지스터를 통합한 300mm 웨이퍼를 소개했다. 이 기술은 ‘GaN 온 실리콘’이라는 명칭으로 불리며, 전력반도체에 활용된다. 인텔은 지난해 열린 IEDM 2022에서 해당 기술을 선보인 바 있으며, 올해는 기술을 직접 구현한 ‘DrGaN’을 공개한다.

인텔 관계자는 “‘DrGaN’ 기술은 미래 컴퓨팅의 높은 전력 밀도 및 효율성 요구사항에 맞춰 전력 공급 솔루션을 구현할 잠재력을 지니고 있다”며 “DrGaN 기반 전력 반도체는 전기차, 스마트폰, 노트북 등 다양한 디바이스에서 활용될 수 있다”고 밝혔다.

전화평 기자 peace201@viva100.com